IIC读写原理详解

478人参与 • 2024-08-06 • 交换机

iic读写原理详解

1.iic简介

iic(inter-integrated circuit),它是一种串行通信总线,可以支持多master和多slave。通过7bit的device address匹配slave。通过scl(时钟总线)和sda(数据总线)传输数据。

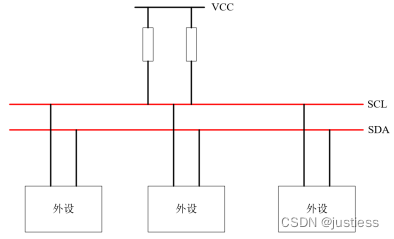

图1 iic架构示意图

如图1所示,scl和sda初始状态需要通过一个电阻上拉,一般上拉电阻值为4.7kω~10kω。通常在日常使用中,可以通过示波器或者iic的协议分析仪去debug。

2.iic接口时序

2.1起始信号

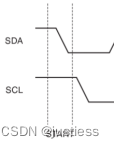

如下图所示,scl为高,sda由高变低,表示iic开始传输,当slave检测到start变开始接收sda数据线上的数据。

图2 start信号

2.2结束信号

如下图所示,scl为高,sda由低拉高,表示iic结束传输,当slave检测到stop便结束接收sda数据线上的数据。表示一次传输结束。

图3 stop信号

2.3 数据传输

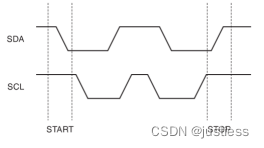

如下图所示,sda必须在scl为高期间保持稳定,在scl为低期间跳变。

图4 数据传输示意图

3.iic读写

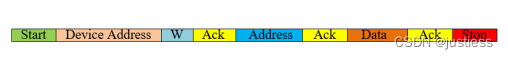

3.1master给slave写数据

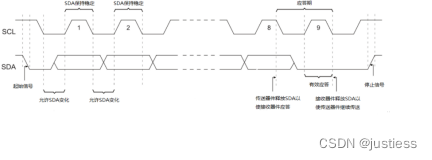

如下图所示,为iic写示意图。

1>.master产生start信号;

2>.master发送7bit的device address和1bit的写控制位;

3>.当master收到slave的ack后,master发8bit的写数据address;

4>.当master收到slave的ack后,master发8bit的data;

5>.如果还需要继续发数据重复步骤4;

6>.当数据发送完成后,master需要发送stop信号给slave。

图5 iic写示意图

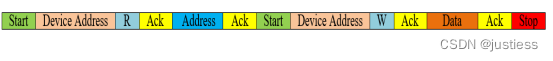

3.2master读slave数据

如下图所示,为iic读示意图。

1>.master产生start信号;

2>.master发送7bit的device address和1bit的写控制位;

3>.master收到slave的ack后,master发8bit的读数据address;

4>.master收到slave的ack后,master重新产生start信号;

5>.master收到slave的ack后,master发送7bit的device address和1bit的读控制位;

6>.master收到slave的ack后,master接收slave发送的8bit的data;

7>.master接收完成数据之后,产生一个时钟周期的nack信号。

8>.master向slave发送一个stop信号,读操作完成。

图6 iic读示意图

您想发表意见!!点此发布评论

发表评论