Xilinx 7系列 FPGA硬件知识系列(三)—— Bank划分及引脚定义

421人参与 • 2024-08-06 • fpga开发

目录

7系列的fpga开始才有hp bank和hr bank,ultrascale fpga有hp bank、hr bank和hd bank,但并不是一个fpga中会同时包含hp/hr/hdbank。

hp:high performance,应用于高速场景,比如ddr或其他高速差分线(不是gtx)

hr:high range,应用于宽范围i/0,最高能够支持到3.3v的电压。

hd:high density,应用于低速i/o的场景,最高速率限制在250m以内,最高电压也是支持到3.3v.

用户bank

fpga的器件管脚按照bank进行划分,每个bank独立供电,以使fpga i/o适应不同电压标准,增强i/o设计的灵活性。每个用户bank包括50个i/o管脚或者24对差分对管脚(48个差分信号),顶端和底端各一个单端管脚。

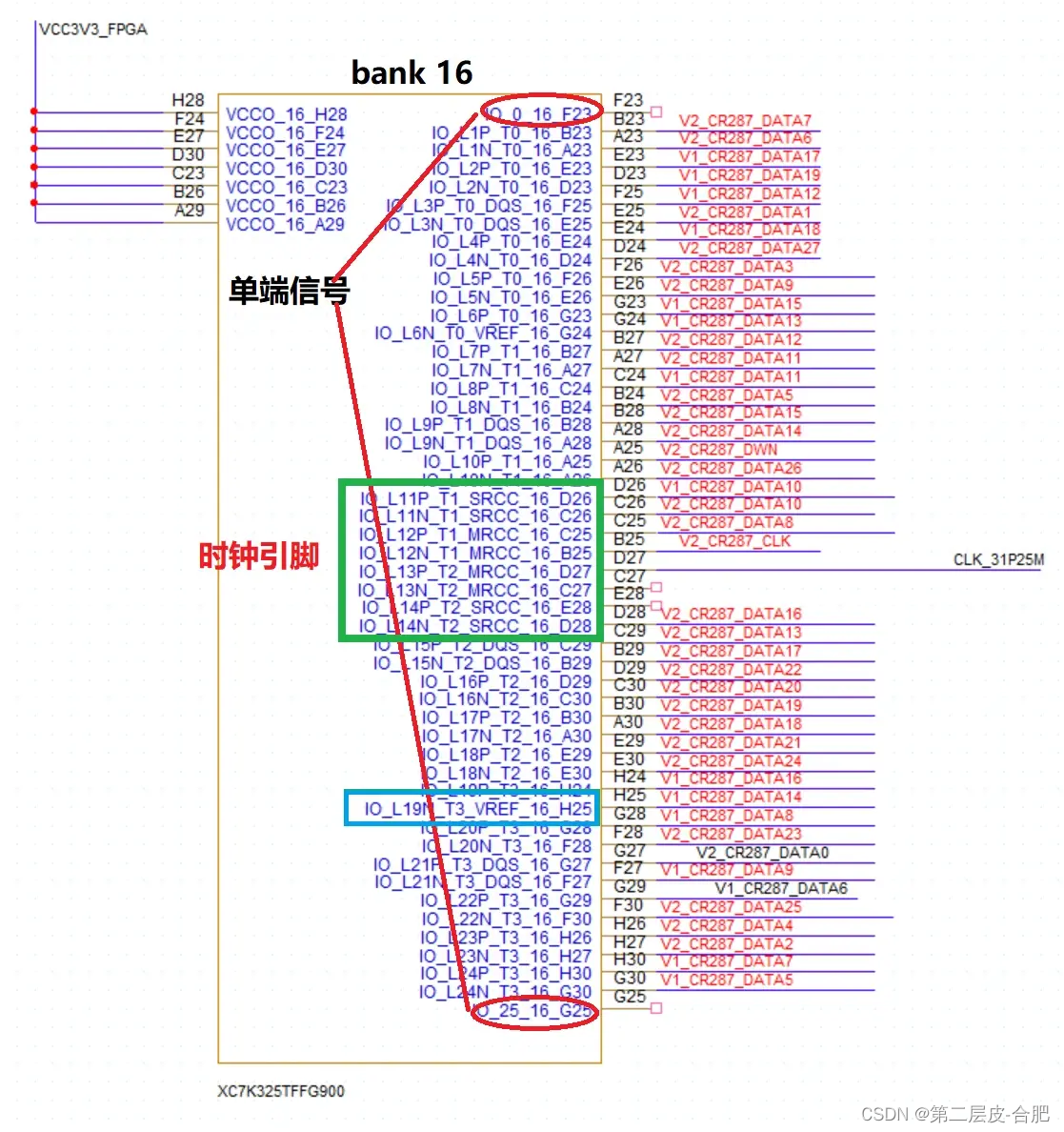

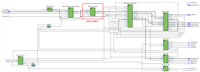

在上图中,我们可以看到红色圈住的两个单端信号,绿色线条圈住的_cc时钟管脚不用作时钟输入时可以作为用户i/o来使用,另外,还可以看到蓝色标记的vref管脚,当该bank i/o用作ddr内存接口时,需要提供伪差分所需的阈值电压,此时_vref_管脚需要接ddr外设要求的参考电压。

notes: 所谓伪差分电平,就是信号在接收端是一个差分的接收器,但其中一端固定接参考电压,而另一端接单端信号线。输入信号电压与参考电压之间进行比较,作为判断输入信号高低的标准。

bank 0(配置bank)

电源

① vcco_0:代表bank 0中所有io所遵循的电平标准,可连接3v3/2v5/1v8/1v5等电压。

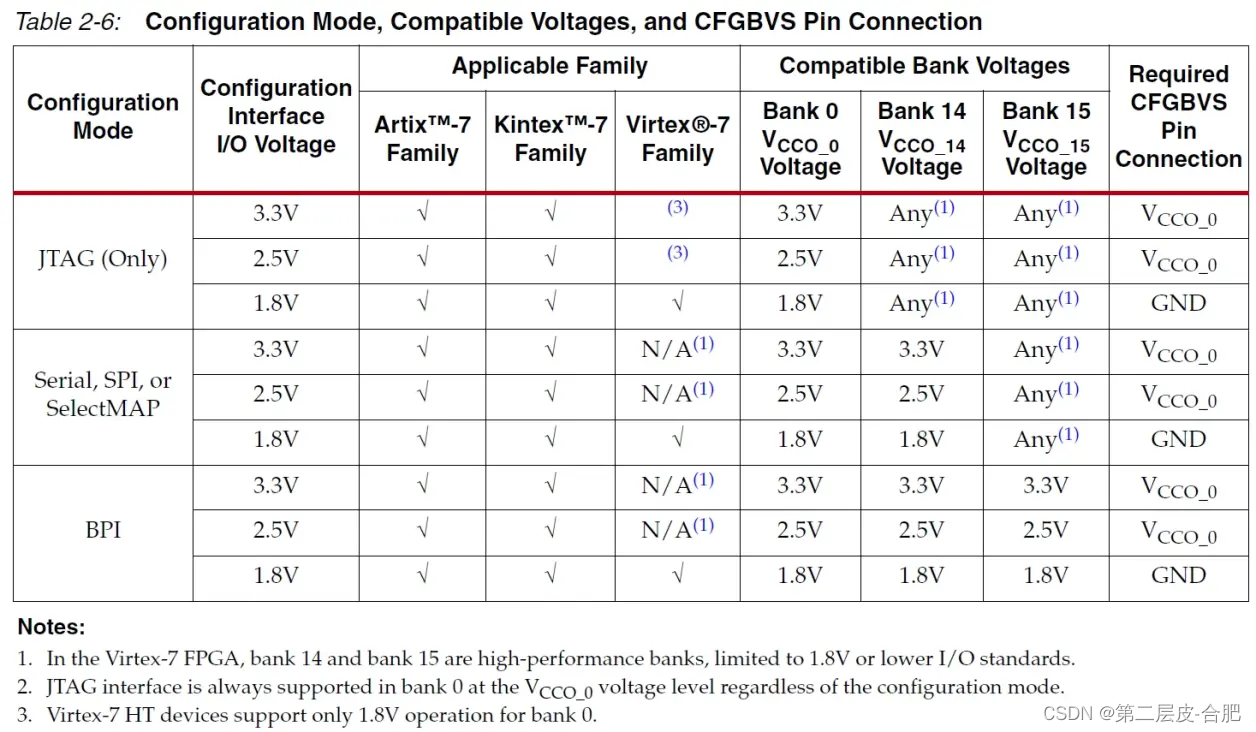

当vcco_0=3v3或2v5时,cfgbvs也必须和vcco_0保持一致;当vcco_0=1v8或1v5时,cfgbvs需要接gnd,cfgbvs一般不需要上下拉电阻,直连就可以。

virtex-7 fpga比较特殊,非ht(virtex-7 ht)器件的bank0和其他s/a/k系列相同,而bank 14/15是hp bank,仅支持1v8以下电平;virtex-7 ht器件无cfgbvs引脚,仅支持1v8电平。

实际应用中,分两种情况:

主spi:该模式下,fpga通过cclk_0输出时钟给flash,考虑到当前spi flash以3v3电源为主,bank 0建议也接3v3,这样能省去电平适配带来的麻烦;

主bpi:该模式下,bpi flash和bank 0之间没有连接关系,只要能找到1v8/1v5供电的bpi flash,理论上bank 0可以连接1v5/1v8/2v5/3v3等电压;

不管是主spi还是主bpi,都会涉及到bank14/15,此时bank14/15的电源需要和bank 0保持一致,这一点需要注意。

② vccbatt_0

该引脚和配置文件加密功能有关,用到该功能时,该引脚需要接外部电池,防止器件掉电后加密功能也失效,ds182中规定电压范围为1v0~1v89,并没有明确规定是1.8v、1.5v还是1.2v;但是用不到加密功能时,xilinx建议接入vccaux(1v8)或gnd。结合来看,电池电压也应和vccaux保持一致,即1v8。spartan-7的7s6/7s15不支持加密功能,该引脚需要接vccaux或gnd。

③ xadc

xadc是xilinx公司的fpga里集成的adc模块、温度传感器、电压传感器的集合。xadc包含2个通道的12位模拟差分输入ad转换器(确保10位可靠精度)、每个通道的采样率都为1msps,分别为adc_a和adc_b。xadc 可测量多达17 个外部模拟通道的输入信号,同时还能对芯片的温度和供电电压进行监测和报警。它是自动循环扫描所有的模拟输入通道,大大地减轻了主芯片的负担。其功能模块如下图所示:

l 内含两个12 位、每秒1 兆采样(1msps)的ad 转换器adc_a 和adc_b。

l xadc 含片上温度传感器,可测试和监控芯片的温度,实现超温报警(ot)。默认的超温报警温度是125°c,用户可以在发生过热报警时及时切断芯片供电以避免损失。用户还可以设定自己定义芯片工作温度范围,当芯片温度超出用户设定的界限时予以报警。

l xadc 内含6 个芯片供电电压传感器,可对芯片供电电源监测和报警。(pl 是fpga 逻辑电路,ps 是cpu 系统)被监测的电源电压如下:

l vccint: pl 内核电压(1.0v)

l vccau: pl 辅助电压(1.8v)

l vccbram: pl bram 电压(1.0v)

l vccpint: ps 内核电压(1.0v)

l vccpaux: ps 辅助电压(1.8v)

l vcco_ddr: ddr ram 电压(1.5v)

用户可以为这些电压设定上、下限,当电压超出用户设定的界限时报警。

xadc 有一路专用的差分模拟输入通道vp/vn,如果不使用vp/vn 时,应该将vp/vn 连接到gndadc引脚。

xadc 另有16 路辅助模拟输入通道。这些输入通道与vp/vn 不同之处是,他们的引脚是模拟/数字复用引脚。如果其中某个引脚被用做模拟输入,该引脚的数字i/o 功能就不可再用。如果辅助模拟输入通道所在的bank 中混合有模拟和数字i/o,该i/o bank 必须由满足所用数字i/o标准所需的电压供电。

辅助模拟输入通道既可以设置成单极性输入,也可以设置成双极性输入。但所有片上传感器(温度和电压)都采用单极性工作模式。

xadc 可对adc 转换结果自动计算和输出平均值,以抑制信号和pcb 板上的噪音。用户可从无平均值计算、16 个样本平均,64 个样本平均或256 个样本平均等四个选项中选取。

xadc 允许延长采样充电时间,将采样充电时间从4 个adcclk 延长至10 个adcclk。当信号源内阻或模拟通道多路器内阻过大影响采样电容获得的信号精度时,加长采样时间可以提高精度。

xadc 内部含有1.25v 的参考电压源。将vref_p0 接模拟地gndadc 就能启用片上参考电压。如果希望得到更高的精度,可以将vref_p0 连接外部精密电压参考ic。

xadc 可基于已知的参考电压源对传感器、adc a 和adc b 的偏移和增益偏差进行校准计算,得到的校准系数存储在xadc 的只读状态寄存器中。随后可以利用这些系数对adc 转换结果进行补偿。

xadc 有128 个16 位寄存器(见图1-1),其中前64 个(daddr[6:0]=00h~3fh)为只读寄存器。用来存放片上传感器、专用模拟通道和辅助模拟通道的当前模数转换结果,同时存储芯片自本次上电以来测量到的最高和最低电压值,分别用adc a 和adc b 测量的电源传感器偏差、以及adc a 和adc b 的自身偏移和增益的校准系数。最后一个地址(3fh)flag 寄存器存储当前报警状态。

地址40h 至7fh 是可读/写寄存器。其中前3 个是xadc 配置和控制寄存器、接着的8 个是辅助模拟通道选择寄存器、再后面是16 个报警阈值预设寄存器。用户通过配置这些寄存器来控制xadc 的行为。剩下的其他寄存器用于工厂测试或未定义,用户不必关注。

为了减轻ps 处理器或fpga 中其他控制系统的负担,xadc 提供了一个叫作sequencer 的模拟通道自动扫描器。sequencer 按预定的顺序自动地逐个接通用户选择的模拟输入通道,执行adc转换并把结果存进xadc 的只读状态寄存器。

fpga 或synq7000 中的pl 逻辑可以通过16 位宽的动态重配置接口(drp)访问xadc 的状态和控制寄存器,通过jtag 口也可以访问这些寄存器。但zynq7000 的ps 是通过axi4-lite 或axi4 stream 接口访问xadc 寄存器的。在vivado 开发环境中用户不需要关心ps 和xadc 互联的细节,只需在运行xadc wizard 时选择axi4-lite 或axi4 stream 就可以了,系统将自动建立两者的互连关系。

ø xadc 的引脚

所有xadc 的专用引脚都在bank0 中,引脚名都以_0 后缀。ug480 图1-2 展示了xadc 的2 种基本连接方法。xadc 由vccaux(1.8v)供电,vccaux 上的低通滤波器用来滤除高频干扰以提高adc 性能。

图中左边的电路采用外部1.25v 精密参考ic 做参考电压,外部参考能提供更好的精度和热漂移性能。铁氧体磁珠用于隔离gndadc 和系统地gnd。ug480 图1-2 右边电路采用片上自带的参考电压源。将vrefp 引脚接到gndadc 引脚就能激活片上参考源。如果只需进行基本的片上温度和电源监测,片上参考已能提供良好性能。100 nf 退耦电容器应尽可能靠近芯片的bga 引脚,以减小寄生电感。

vccadc_0:xadc 中adc 和其他模拟电路的模拟电源引脚,电压和vccaux保持一致,建议单独供电或通过滤波电路(电感等)连到vccaux上,不使用时也需要接vccaux;

gndadc_0:xadc的模拟接地引脚,应该通过磁珠连接到系统gnd。在一个混合信号系统中,如果可能的话,此引脚应该连到在一个模拟的接地平面上,在这种情况下就可以不需要铁氧体磁珠。即使xadc 不用,也应始终将此引脚连接到gnd。

vp_0/vn_0:xadc专用差分输入引脚(专用是对比其他xadc模拟输入来说,该引脚不能用作普通io,其他的都可以),不使用时接gnd;

vrefp_0:电压基准,此引脚可连接到外部1.25v 精确参考ic(±0.2%或12 位的±9 lsb),以获得adc 的最佳性能。应将其视为模拟信号,与vrefn 信号一起提供1.25v 差分电压。如果将此引脚连接到gndadc,芯片内参考源(12 位时为±1%或±41 lsb)被激活。如果没有提供外部引用,这个引脚应该应始终连接到gndadc。

vrefn_0:电压基准gnd,该引脚应与外部1.25v 精确参考ic(±0.2%)的地引脚相连,以获得最佳的adc 性能。应将其视为模拟信号,与vrefp 信号一起提供差分1.25v 电压。即使没有提供外部参考,此引脚也应始终连接到gndadc。

ad0p_ toad15p:辅助模拟输入/数字io,这些是多功能引脚,可以支持16 个模拟的正输入端,也可以用作常规数字i/o(见图1-1)。当不被用作模拟输入时,这些引脚可以像其他任何数字i/o 一样使用。

ad0n_ toad15n:辅助模拟输入/数字io,这些是多功能引脚,可以支持16 个模拟的负输入端,也可以用作常规数字i/o(见图1-1)。当不被用作模拟输入时,这些管脚可以像其他任何数字i/o 一样使用。

dxp_0/dxn_0:dxp、dxn 为内部热敏二极管温度传感器引脚,在bank0热二极管被允许接入使用dxp和dxn引脚,结合外部温度监控电路可实现对fpga芯片结温的监控,不用时接系统gnd。在设计该部分电路时,可以使用max6642替代热敏二极管。大多数热敏二极管温度传感器,包括max1617和max6654,与二极管都有两个连接点:dxp和dxn。dxp连接至热敏二极管的阳极,源出二极管偏置电流。dxn吸入偏置电流,并将阴极偏置在0.7v左右。

从上图可以看出,fpga上电后,xadc可以监测fpga内的温度以及所有的fpga电压,还可以接收来自fpga专用模拟差分管脚vp_0/vn_0的模拟差分信号(不可以作为普通user i/o),也可以接收fpga其他普通数字/模拟混合管脚vauxp/vauxn[15:0]的16路模拟差分输入(不使用的时候可以作为普通的user i/o),因此xadc可以最多处理17路外部模拟信号。

xadc的输出通过jtag口可以直接被fpga开发工具读取并用vivado开发工具实时在线监测,也可以由用户调用xadc硬核,并用代码在fpga里实现实时获取信息。另外,如果咱们觉得用代码实现有困难,那还可以借助xilinx core generator生成xadc的ip核,只要配置好之后加载到fpga逻辑代码里也可以工作,自己写代码和调动ip核这两种方式都可以方便的供用户自己读取fpga的温度、电压以及外部输入的模拟信号等信息。

xadc的端口如下图所示,其每个端口的具体含义请参考ug480的p19~p20。

专用模拟输入vp/vn

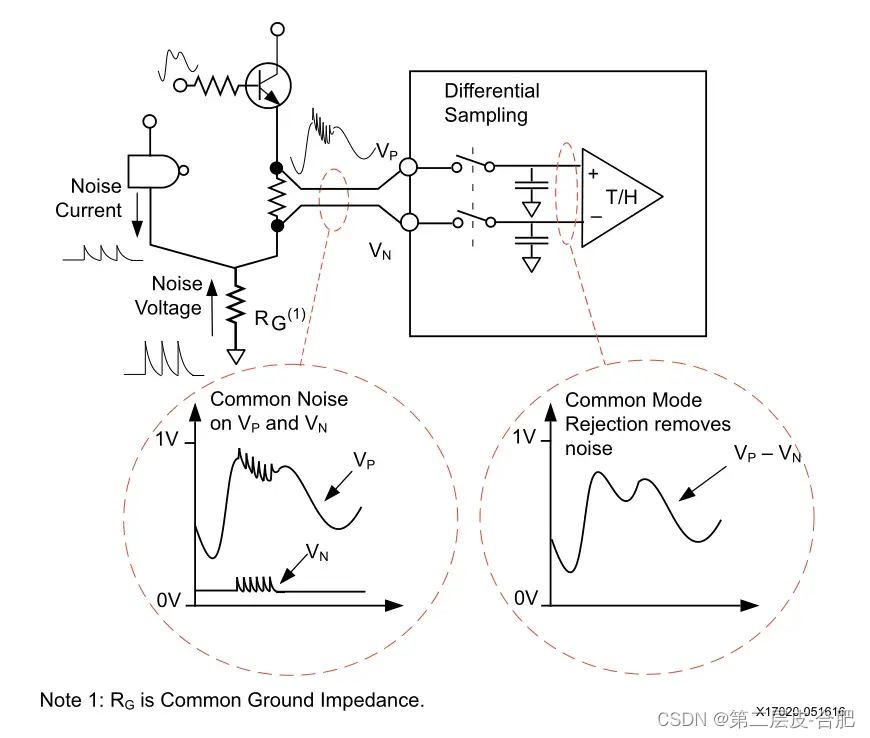

专用模拟输入vp/vn 采用差分采样方案,以减少共模噪声信号的影响。pcb 的公共地阻抗将数字电路的开关电流噪音耦合到模拟系统,其幅度可达100 毫伏或更高。这对于adc 来说相当于数百个lsb,因此会导致很大的测量误差。差分采样方案在两个输入端(vp/vn)对含共模噪声的信号进行采样。adc 的前置放大器的高共模抑制比有效地抑制了共模噪声信号,送到adc 输入口的只剩下vp 和vn 之间的差模信号。所以用户如果要获得高共模抑制比,应采用专用模拟输入通道vp/vn。

ug480 图2-4 共模噪音抑制

辅助模拟输入通道

辅助模拟输入(vauxp[15:0]和vauxn[15:0])是与常规数字i/o 引脚共享的模拟输入引脚。

辅助模拟输入通道引脚的iostandard 必须与所在bank 的数字i/o 标准所要求的电压兼容(在xdc 约束文件中声明),其输入的模拟信号幅度不应超过数字i/o bank 的电源电压。只有被启用为辅助模拟输入的引脚才具有模拟输入属性,其他引脚仍然保留数字i/o 属性。

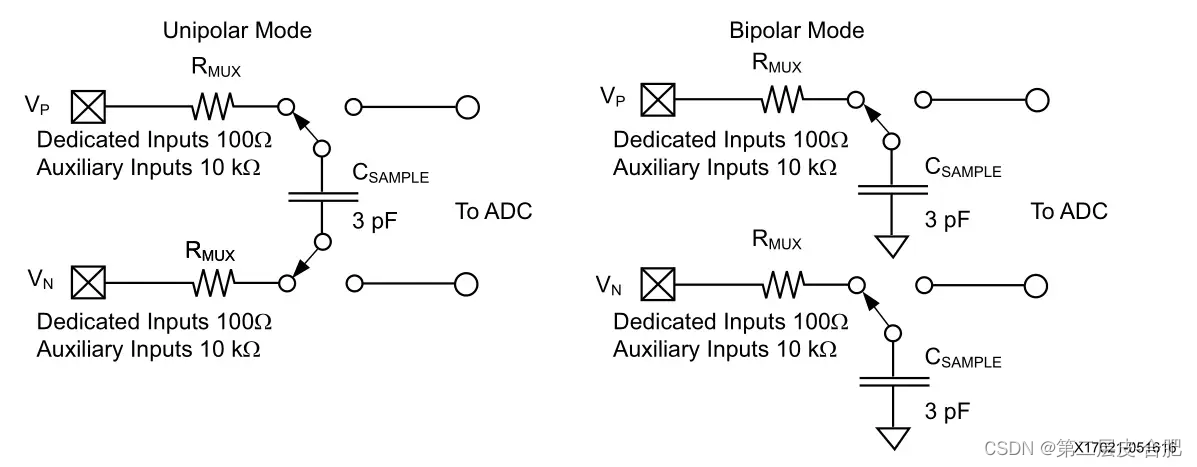

ug480 图2-5 是辅助模拟输入通道单极性和双极性输入模式的等效电路。

单极性输入时只有一个采样电容,双极性输入时有2 个采样电容。在adc 采集阶段,采样开关闭合,采样电容充电至模拟输入信号源的电压,然后采样开关切换连接adc。

采样电容器充电至最终值(达到输入信号值±0.5 lsbs)所需的时间取决于采样电容器的大小、模拟多路开关的电阻和外部信号源阻抗。

ug480 图2-5 模拟输入的等效输入电路

根据测算,专用模拟通道(vp/vn)所需最小采样时间为3ns,而辅助模拟通道(vauxp[15:0]和vauxn[15:0])因为有一个大约10k的开关电阻,最小采样时间是300ns。任何额外的外部电阻(如去假频滤波器或电阻分压器)都会增加采集时间要求。

单极性输入要求

测量单极性模拟输入信号时,adc 必须设置成单极性输入模式。通过写入配置寄存器0 来选择此模式。单极性输入时,以专用模拟输入(vp/vn)为例,信号必须满足以下要求:

vp 和vn 必须始终高于gndadc

vp 必须始终高于vn

vp 和vn 之间最大幅度差是1.0v(adc 的满标电压)

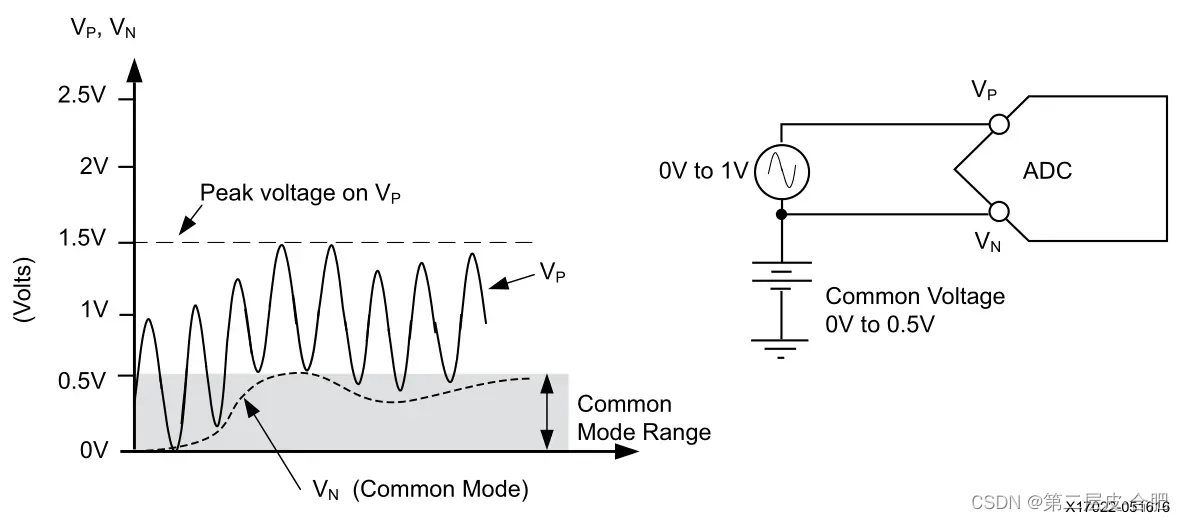

vn 上的共模信号可以在0 v到+0.5 v之间变化(相对于gndadc 测量),所以vp 上的最大信号不得高于+1.5 v。

vn 通常连接到本地接地或共模信号上

ug480 图2-6 说明了这种关系:

ug480 图2-6 单极性输入信号要求

双极性输入要求

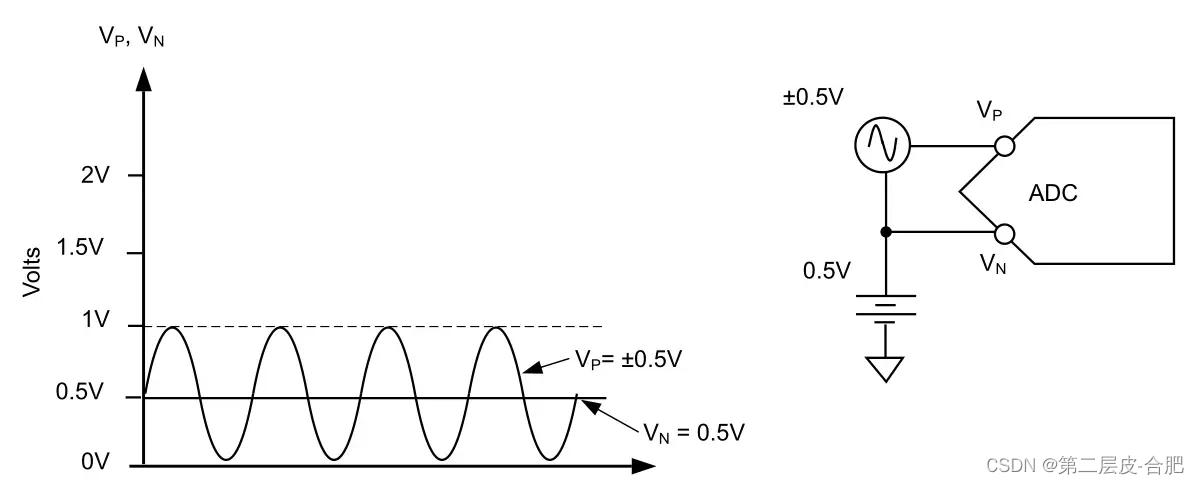

双极性输入信号具有以下属性:

vp 和vn 相对关系不总是vp>vn,两者的关系是交替变化的。vp 可能高于vn,但vp 也可能低于vn,但vp 和vn 都必须高于地电平。例如平衡电桥的输出信号就具有这种属性,但2 个输出端上有一个高于公共地的共模电压。

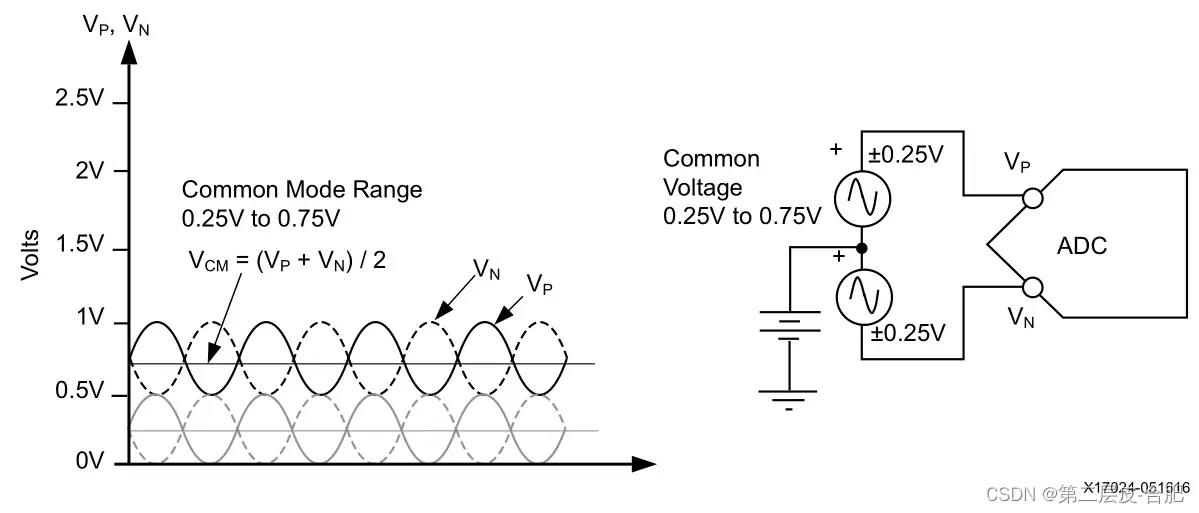

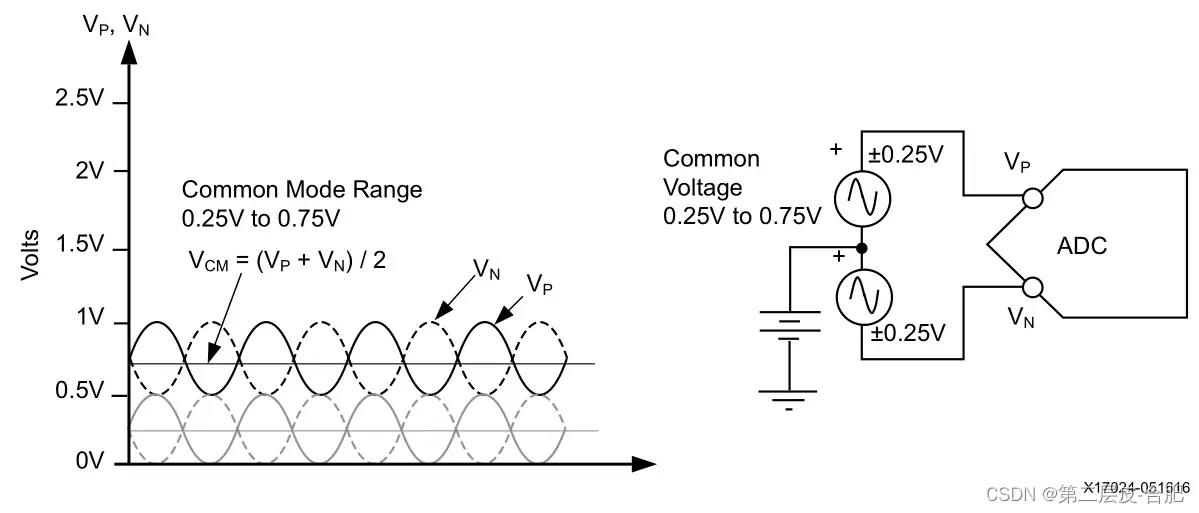

vp 和vn 是一个相对于gndadc 的交流电压。这种情况就必须设法引入一个共模电压,将vp 和vn都拉到gndadc 电平以上。在上述第一种情况,因为xadc 的满标电压是1.0v,共模电压不应超过0.5 v。以平衡电桥为例,电桥的2 个输出上的共模电压应该是0.5v,如下图所示。将平衡电桥的一个输出连接到vn,vp 在vn 的上下摆动,其幅值<±0.5v。

ug480 图2-7 双极性输入信号要求

vp 和vn 如果是相对于gnd 的交流信号,则可以用lt1991-1(增益=1)将其转换成双极性差分输出信号,并在lt1991-1 的vcom 引脚上加1 个0,5v 的共模电压。结果输出就是在0.5v 共模电压基线上变化的差分信号。见下图。

ug480 图2-8差分输入信号要求

jtag

tck_0:测试时钟输入,连外部仿真器,建议加防静电措施(tvs管),含驱动电路时,注意输入弱上拉(例如10kω),保持未接仿真器时为高电平;

tms_0:测试模式输入,其他同tck_0;

tdo_0:测试数据输出,连外部仿真器,级联时连接后级tdi_0引脚,建议加防静电措施(tvs管);

tdi_0:测试数据输入,连外部仿真器,级联时链接前级tdo_0引脚,建议加防静电措施(tvs管);

大多数应用中,不会涉及到多个fpga,即使涉及到了,也不会级联,而是每个器件都会预留一个jtag调试口。若涉及到多个fpga级联的情况,常规的做法是多个fpga共用tck/tms,前级tdo接后级tdi,需要考虑驱动能力、走线等因素。

在硬件电路上,jtag的4个引脚都需要串联33ω的电阻(这个很重要),然后v2和v4系列的fpga tck需要下拉4.7k或10k,在7系列的fpga中四个引脚都上拉4.7k或10k。并且上拉或者下拉都是在fpga的输入端,tdi、tms、tck都是fpga的输入端,而tdo是fpga的输出端。

⑤ 配置

配置引脚的接法和器件采用的配置模式相关,当前常用的配置模式是主spi和主bpi模式,主串、主并、从串、从并模式基本上不用,仅介绍两种常用模式下的连接方法。

cclk_0:主spi模式下,该引脚为时钟输出引脚,连接spi flash的时钟输入引脚,需要考虑信号完整性(源端匹配+上下拉);主bpi模式下不使用,可以悬空;

init_b_0:该引脚刚上电时为低电平,直到初始化完成,变为高阻态,需要外接上拉电阻到vcco_0(≤4.7kω),变为高电平后开始采样m[2:0]引脚,执行后续操作;该引脚可以由外部控制拉低,以推迟fpga配置过程;在主bpi场合下,可以将该引脚接到bpi flash的/reset引脚上,当检测到配置数据错误时,触发bpi flash复位;(若整个系统上电,该电路板暂时不上电,就采用init_b_0来复位)。

program_b_0:该引脚上的低电平表示需要重新配置fpga,需要外接上拉电阻到vcco_0(≤4.7kω),通常可以外接按键来提供手动复位功能;(若整个系统上电,该电路板也上电,就采用program_b_0来复位)。

cfgbvs_0:高电平(vcco_0)代表2v5/3v3电平(bank 0以及配置期间的bank 14/15),低电平(gnd)代表1v8/1v5电平标准;

done_0:该引脚上的高电平代表配置完成,内部含10kω上拉电阻(仅7系列),外部可以不接330ω上拉电阻(仅7系列),考虑到兼容之前系列fpga,也可以保留该外部上拉电阻;

m0_0/m1_0/m2_0:决定了fpga的启动模式,直连vcco_0/gnd或通过上下拉电阻连接(≤1kω),主spi对应001,主bpi对应010,jtag对应101,建议预留jtag模式(101),fpga起不来又连不上仿真器的情况下可以用来恢复。

bank 14(hr bank)

电源

vcco_14:可接1v2/1v5/1v8/2v5/3v3等多种电压,但是主spi/主bpi模式下配置过程涉及到该bank上的某些引脚,需要和vcco_0保持一致。

普通io

普通io指的是该引脚只做io用,没有其他功能复用情况,bank 14共有两个普通io,io_0_14和io_25_14,即第一个和最后一个。

配置io

仅针对主spi/主bpi情况说明,其他情况基本上用不到。

d[15:00]:主spi ×1/×2模式用到d[01:00](mosi/din),主spi ×4模式用到d[03:00],主bpi模式下用到d[15:00];

a[15:00]:主spi模式下不使用,主bpi模式下用作低16位地址线;

pudc_b:配置期间io内部上拉使能引脚,低电平使能上拉,高电平禁止上拉,可以直连或通过上下拉电阻(≤1kω)连接,一般选择上拉,以保证配置期间io为三态,不输出任意波形;

emcclk:外部时钟输入引脚,主spi模式下,可以切换替代cclk_0功能,达到提速的目的,使用时需要外接晶振;

fcs_b:主spi/主bpi模式下,作为片选功能连接到flash的/cs引脚,需要外接上拉电阻(≤4.7kω)到vcco_14;

rdwr_b:仅并行模式下使用,主spi/bpi模式下不使用;

dout_b/cso_b:级联功能引脚,主spi x1级联模式下(x2/x4模式不支持级联),连接后级的din引脚,组成菊花链;主bpi级联模式下,连接后级的csi_b引脚,需要外接330ω上拉到vcco_14上(主spi x1级联模式不需要外接上拉电阻);

csi_b:仅并行级联模式下使用,主spi/主bpi模式下不使用;

特别说明下,主bpi级联模式中,第一个器件为主bpi模式,后级所有器件都为从并模式,首器件通过fcs_b连接外部flash(不用csi_b),将cso_b连到后级csi_b中,后级其他器件通过csi_b和cso_b组成菊花链。

时钟io

ø srcc:共2组4根时钟输入,可驱动bufio/bufr/bufg;

ø mrcc:共2组4根时钟输入,可驱动bufio/bufr/bufmr/bufg。

其他io

dqs:ddr专用dqs引脚;

vref:ddr专用电压参考引脚。

bank 15(hr bank)

电源

vcco_15:主spi模式不涉及该bank,可接1v2/1v5/1v8/2v5/3v3等多种电压;主bpi模式配置过程涉及该bank,需要和vcco_0保持一致。

普通io

共有三个普通io,io_0_15/io_l6p_t0_15/io_25_15。

配置io

adv_b:主spi模式下不使用;主bpi模式下,针对支持地址有效功能的flash,连接到该flash的adv引脚,外接上拉电阻(≤4.7kω)到vcco_15,针对不支持地址有效功能的flash,不要使用该引脚;

a[28:16]:主spi模式下不使用;主bpi模式下,用作高13-bit地址线;

foe_b:主spi模式下不使用;主bpi模式下,连接bpi flash的/oe引脚,外接上拉电阻到vcco_15(≤4.7kω);

fwe_b:主spi模式下不使用;主bpi模式下,连接bpi flash的we引脚,外接上拉电阻到vcco_15(≤4.7kω);

rs1/rs0:仅在使能回读模式或远程重配置的情况下才会用到,比如我们需要启动不同版本代码的时候,可以通过配置这两个脚来实现。

时钟io

同bank 14。

其他io

ad[n]p/n:xadc的模拟输入引脚;

dqs:ddr专用dqs引脚;

vref:ddr专用电压参考引脚。

bank 12/13/16/17/18(hr bank)

电源

vcco_12/13/16/17/18:可接1v2/1v5/1v8/2v5/3v3等多种电压,根据需要选择。

普通io

共32个普通io。

时钟io

同bank 14。

其他io

同bank 14。

bank 32/33/34(hp bank)

电源

vcco_32/33/34:可接1v2/1v5/1v8等多种电压,根据需要选择。

普通io

共30个普通io(少了两个vrp/vrn引脚)。

时钟io

同bank12,4个srcc+4个mrcc。

其他io

包含dqs/vref/vrp/vrn等ddr/dci专用引脚。

notes:

7系列的fpga开始才有hp bank和hr bank,ultrascale fpga有hp bank、hr bank和hd bank,但并不是一个fpga中会同时包含hp/hr/hdbank。

hp:high performance

hr:high range

hd:high density

hp bank,应用于高速度比较高的场景,比如ddr或者其它高速差分总线(不是gtx),由于速率比较高,bank电压最高也只能到1.8v。

hr bank表示支持wider range of i/o standards,最高能够支持到3.3v的电压。

hd bank应用于低速i/o的场景,最高速率限制在250m以内,最高电压也是支持到3.3v.

hr和hp banks的lvds电平

当两个bans的i/o口作为lvds电平时,hr banks的i/o电压vcco只能为2.5v,hp banks的i/o口电压为1.8v。两个banks支持lvds的标准不同,hr i/o banks的i/o只能分配lvds_25标准,hp分配为lvds标准。lvds_25的直流特性如下表所示:

对比上述两表可知,虽然lvds_25和lvds的bank的工作电压不同,但是lvds电平的直流特性一样。高速ad/da的lvds工作电压一般为1.8v,在初次使用7系列时,一些硬件工程师可能担心:hr bank的工作电压为2.5v,那么hr bank的lvds是否可以直接连接工作电压为1.8v的ad/da的lvds接口,通过查看它们lvds的直流特性,可以放心的连接。

下图是7系列fpga hp bank和hr bank支持的特性:

selectio管脚可根据各种i/o标准 (包括单端和差分)进行配置。

单端i/o标准包括lvcmos、lvttl、hstl、sstl、hsul和pod等。

差分i/o标准包括lvds、mini_lvds、rsds、ppds、blvds、tmds、slvs、lvpecl、sub_lvds以及差分 hstl、pod、hsul和sstl等。

bank 115(gtx bank)

校准

mgtavttrcal和mgtrref,用于gtx内部校准,mgtavttrcal直连1.2v(同mgtavtt),mgtrref通过100ω电阻连接mgtavttrcal。若不用gtx功能,应连接gnd。

含两组差分时钟引脚,mgtrefclk[n]p/n,接入外部差分时钟(需要电容耦合)。若不用gtx功能,应悬空。

数据

含4组差分收发引脚,mgtxtxp/n[n]、mgtxrxp/n[n],使用时需要电容耦合。若不使用gtx功能,接收端可以选择悬空(偏置)或连gnd(未偏置),发送端应悬空。

bank 116/117/118(gtx bank)

无校准引脚,其他同bank115。

gtx电源

mgtavcc:1.0v(≤10.3125ghz),1.05v(>10.3125ghz);

mgtavtt:1.2v;

mgtvccaux:1.8v;

上下电时序要求:先上vccint和mgtavcc(两者之间无特殊要求,可以同时上),然后上mgtavtt,mgtvccaux无特殊要求,下电时序和上电时序相反;

不使用gtx功能时,供电引脚可以悬空或连gnd。

非gtx电源

ø vccint:fpga内部核心电压,其不损坏fpga器件的范围为-0.5v~1.1v,正常工作电压为0.97v~1.03v,推荐工作电压为1.0v,并且根据速度等级变化为1.0v/0.95v(-2li)/0.9v(-2le);

ø vccbram:内部block ram的供电电压,其不损坏fpga器件的范围为-0.5v~1.1v,正常工作电压为0.97v~1.03v,推荐工作电压为1.0v。并且根据速度等级变化为1.0v/0.95v(-2li)/0.9v(-2le);

ø vccaux:辅助供电电压,其不损坏fpga器件的范围为-0.5v~2.0v,正常工作电压为1.71v~1.89v,推荐工作电压为1.8v;

ø vccio:对于hr bank的接口电压来说,需要与外部器件的信号电平保持一致,其不损坏fpga器件的范围为-0.5v~3.6v。正常工作电压为1.14v~3.465v。推荐工作电压与外部信号电平一致即可。对于hp bank的接口电压来说,需要与外部器件的信号电平保持一致,其不损坏fpga器件的范围为-0.5v~2.0v。正常工作电压为1.14v~1.89v。推荐工作电压与外部信号电平一致即可。

ø vccaux_io:io辅助电压,其不损坏fpga器件的范围为-0.5v~2.06v,正常工作电压为1.14v~1.89v/2.06v,推荐工作电压为1.8v/2v;

ø vccadc:xadc的供电电压,其不损坏fpga器件的范围为-0.5v~2.0v,正常工作电压为1.71v~1.89v,推荐工作电压为1.80v。

ø mgtavcc:gtx收发器核心电压,其不损坏fpga器件的范围为-0.5v~1.1v,正常工作电压为0.97v~1.08v,推荐工作电压为1.00v。

ø mgtavtt:gtx收发器终端匹配电压,其不损坏fpga器件的范围为-0.5v~1.32v,正常工作电压为1.17v~1.23v。推荐工作电压为1.2v。

ø mgtvccaux:gtx收发器辅助电压,其不损坏fpga器件的范围为-0.5v~1.935v,正常工作电压为1.75v~1.85v,推荐工作电压为1.8v。

ø mgtavttrcal:gtx收发器校正电压,其不损坏fpga器件的范围为-0.5v~1.32v,正常工作电压为1.17v~1.23v,推荐工作电压为1.2v。

官方推荐的上电顺序依次为vccint、vccbram、vccaux、vccaux_io、vcco,断电顺序和上电顺序正好相反。另外如果vccint和vccbram电源轨一致,则可同时上电/断电。vccaux_io、vccaux与vcco电源轨一致也可同时上电/断电。其它电源轨则无上电顺序。gtx收发器的上电顺序为vccint、mgtavcc、mgtavtt或者mgtavcc、vccint、mgtavtt。断电顺序正好相反。mgtvccaux无顺序。

作者:硬件光阴 https://www.bilibili.com/read/cv26635057/?spm_id_from=333.999.0.0 出处:bilibili

您想发表意见!!点此发布评论

发表评论